Initially first Half Adders circuit will be used to add inputs A and B to produce a partial sum. CLA Adders generate the carry-in for each full adder simultaneously by using simplified equations involving Pi Gi.

Design 4 Bit Voting Combinational Eircuit That Has Two Outputs One Output To Indicate Mejority And Snother To Indicate A Tie Vot Homework Help Equations Logic

This way 4-bit adder can be made using 4 full adders.

. The full adder is a combinational circuit so that it can be modeled in Verilog language. Single-bit Full Adder circuit and Multi-bit addition using Full Adder is also shown. However to add more than one bit of data in length a parallel adder is used.

Half adder is the simplest of all adder circuit but it has a major disadvantage. This is a truth table. Mainly there are two types of Adder.

Full Adder Truth Table with Carry. The output carry is designated as C OUT and the normal output is designated as S. But in Full Adder Circuit we can add carry in bit along with the two binary numbers.

Database Management System. SR Flip Flop Construction Logic Circuit Diagram Logic Symbol Truth Table Characteristic Equation Excitation Table are discussed. Database Management System.

Full Adder Design on FPGA using Verilog. Advantages of Carry Look Ahead Adders. Know all about the OR Gate here.

A parallel adder is an arithmetic combinational logic circuit that is used to add more than one bit of data simultaneously. The role of C pin is to determine the overflow in the unsigned numbers. From the above half subtractor truth table we can recognize that the Difference D output is the resultant of the Exclusive-OR gate and the Borrow is the resultant of the NOT-AND combinationThen the Boolean expression for a half subtractor is as below.

Truth table K-Map and minimized equations for. The two inputs are A and B and the third input is a carry input C IN. Half Adder and Full Adder.

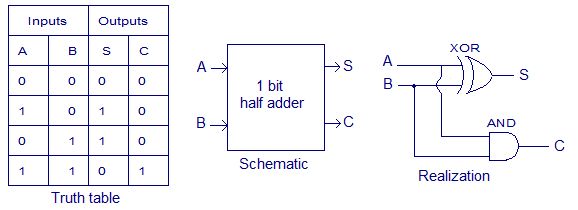

If A and B are the input bits then sum bit S is the X-OR of A and B and the carry bit C will be the AND of A and B. A truth table is a mathematical table used in logicspecifically in connection with Boolean algebra boolean functions and propositional calculuswhich sets out the functional values of logical expressions on each of their functional arguments that is for each combination of values taken by their logical variables. This circuit can be constructed by combining two Half Adders.

A 16 bit CLA adder can be constructed by cascading four 4 bit adders with two extra gate delays while a 32 bit CLA adder is formed when two 16 bit adders are cascaded to form one system. From the above truth table For the different functions in the truth table the minterms can be written as 1247 and similarly for the borrow the minterms can be written as 1237. In this project a simple 2-bit comparator is designed and implemented in Verilog HDL.

Half Adder and Full AdderIn half adder we can add 2. 4-bit Full adder n bit adder can be made using n full adders in series. In particular truth tables can be used to show whether a.

As the full adder circuit above is basically two half adders connected together the truth table for the full adder includes an additional column to take into account the Carry-in C IN input as well as the summed output S and the Carry-out C OUT bit. A full adder adds two 1-bits and a carry to give an output. The half adder can add only two.

The truth table of the Full Adder Circuit is shown below. The inter connection of 4 full adder in 4bit parallel adder is shown below Let us examine the justification of the above circuit by taking an example of addition of two 4 bit binary numbers. Create circuit from truth table.

A Verilog code for a 4-bit Ripple-Carry Adder is provided in this project. 4 a Truth Table of Full Adders Circuit b K-Map Simplification of Truth Table. The log ical exp ression for half-subtractor is.

Half Adder and Full Adder circuits is explained with their truth tables in this article. A Flip Flop is a memory element that is capable of storing one bit of information. Before going into this subject it is very important to know about Boolean Logic and Logic Gates.

If C1 then there is a carry out in case of addition indicating unsigned overflow or a borrow in during subtraction. A Flip Flop is a memory element that is capable of storing one bit of information. The logical expression for the two outputs sum and carry are given below.

In half adder we can add 2-bit binary numbers but we cant add carry bit in half adder along with the two binary numbers. From this it is clear that a half adder circuit can be easily constructed using one X-OR gate and one AND gate. JK Flip Flop Construction Logic Circuit Diagram Logic Symbol Truth Table Characteristic Equation Excitation Table are discussed.

Karnaugh Map to Circuit. Design of Full Adder using Half Adder circuit is also shown. We can also add multiple bits binary numbers by cascading the full adder.

The decoder includes three inputs in 3-8 decoders. Based on the truth table we can write the minterms for the outputs of difference borrow. For adding two 4 bit binary numbers we have to connect 4 full adders to make 4 bit parallel adder.

For a boolean function of N inputs there are 2 N possible input combinations. Full Adder Logic Diagram. 4 bit adder-subtractor circuit.

Full Adder Design on FPGA using VHDL. These full adders can be used for adding n bit number sif n number of full adders are connected in a cascaded setup with c out connected to the C in of the next full adder. A half adder adds two binary numbers.

Here is a brief idea about Binary adders. The Full Adders circuit can be implemented using the Truth Table and K-Map simplification. Karnaugh Map to Circuit.

As there is no previous. A B are the input variables for two-bit binary numbers Cin is the carry input and Cout is the output variables for Sum and Carry. The main difference between a half adder and a full adder is that the full-adder has three inputs and two outputs.

Consider the advanced version of 4-bit adder-subtractor circuit which comes with carry C bit and overflow V bit. In previous tutorial of half adder circuit construction we had seen how computer uses single bit binary numbers 0 and 1 for addition and create SUM and Carry outToday we will learn about the construction of Full-Adder Circuit. Let us add 1011 with 1101.

A parallel adder adds corresponding bits simultaneously using full adders. Mainly there are two types of Adder.

One Way We Could Expand The Capabilities Of Either Of These Two Counter Circuits Is To Regard The Q Outputs As Another Set Of Four B Counter Expand Binary

Verilog Code For Pipelined Mips Processor Coding Processor Math

Vhdl Code For 2 To 4 Decoder All About Fpga Coding Computer Science Tutorial

Moore State Machine Vhdl Code Coding Detector States

Carry Save Adder Vhdl Code Coding Carry On Save

Binary Multiplier Types Binary Multiplication Calculator Binary Electronic Schematics Multiplication

Experiment Write Vhdl Code For Realize All Logic Gates Logic Experiments Electronic Circuit Design

Verilog Code For Button Debouncing Coding Buttons Electronics Projects

Binary Adder Subtractor Construction Types Applications Electronic Engineering Electronic Schematics Engineering Technology

Vhdl Code For Full Adder Coding Computer Science Binary Number

4 Bit Ripple Carry Adder Vhdl Code Coding Ripple Carry On

Vhdl Code For Full Adder Coding Computer Science Neon Signs

2 Bit Multiplier 2 Bits Bits Circuit

Pin On Electronic Circuit Design

Kunci Jawaban Tes Koran Koran Kunci

Full Adder Schenatic Electronics Electrical Electronics Circuit Electricity Electrical Components